## <u>UNIT-I</u>

#### The 8086 Microprocessor

Introduction to 8086 – Microprocessor architecture – Addressing modes - Instruction set and assembler directives – Assembly language programming – Modular Programming - Linking and Relocation - Stacks - Procedures – Macros – Interrupts and interrupt service routines – Byte and String Manipulation.

## 1. Introduction to 8086

## 8086-HARDWARE ARCHITECTURE

## AUQ: Explain the features of 8086 microprocessor. (May 2011, 8 Marks)

The features of 8086 are:

- The 8086 is a 16 bit processor

- The 8086 has a 16 bit data bus

- The 8086 has a 20 bit address bus

- Direct addressing capability 1M byte of memory $(2^{20})$

- It provides fourteen 16 bit register

- 24 operand addressing modes

- Bit, byte, word and block operations.

- 8 and 16 bit signed and unsigned arithmetic operations including multiply and divide

- Four general purpose 16 bit registers: AX, BX, CX, DX

- Two pointer group registers: stack pointer (SP), Base pointer(BP)

- Two index group registers: source index (SI), destination index (DI)

- Four segment registers: code segment (CS), Data segment (DS), Stack segment (SS), Extra segment(ES)

- 6 Status flag and 3 control flags.

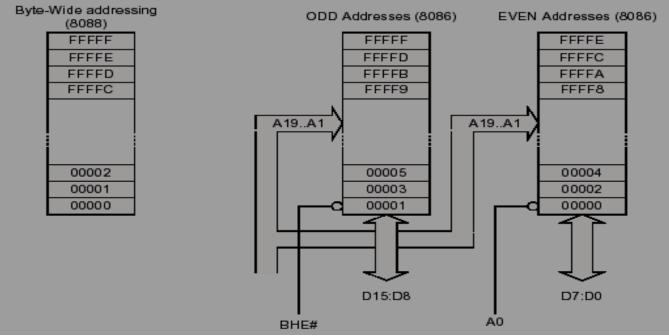

- Memory is byte addressable- each address stores an 8 bit value.

- Address can be up to 32 bit long, resulting in 4GBof memory.

- Range of clock rates: 5MHZ for8086, 8MHZ for8086-2, 10MHZ for8086-1

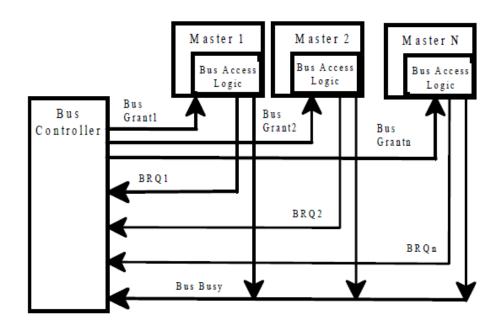

- Multibus system compatible interface

- Available in 40 pin plastic package and lead cerdip.

- 2. <u>8086 Microprocessor Architecture:</u>

# AUQ: Explain the internal architecture of 8086 microprocessor.(Dec-2003,04,06,08,11,12,13, May-2003,05,07,08,10,11,15, May 2016, Dec 2016, May 2017)

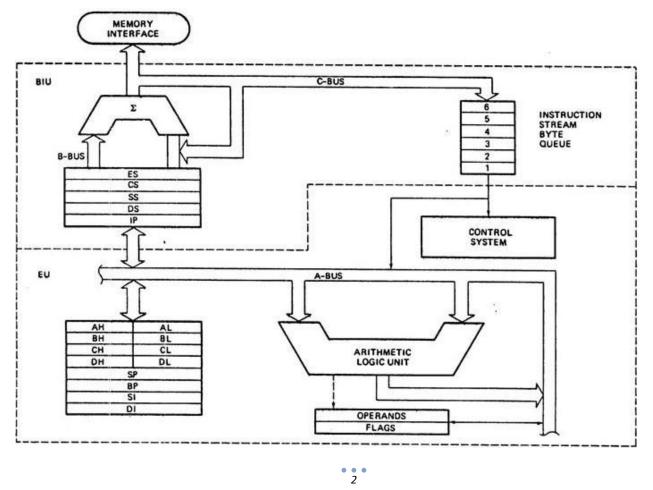

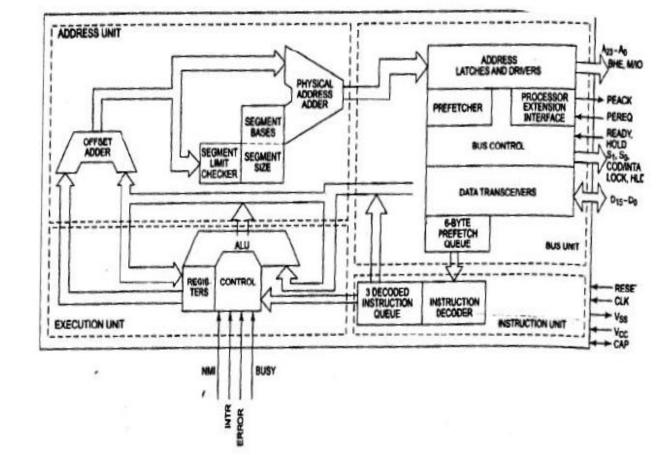

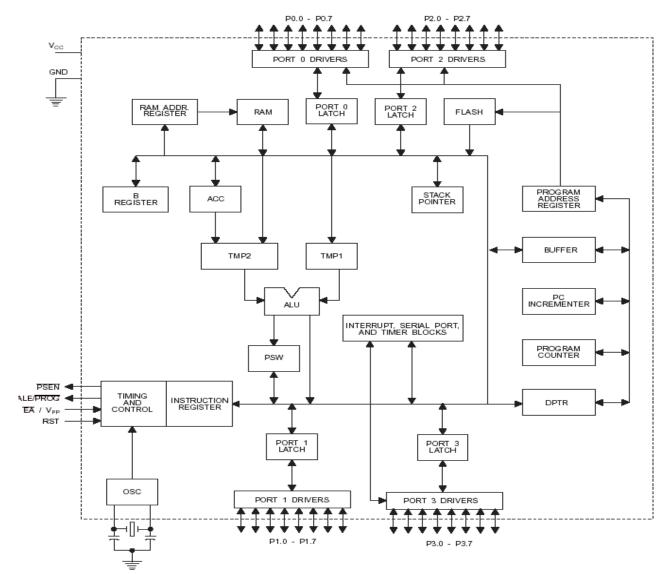

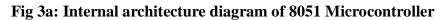

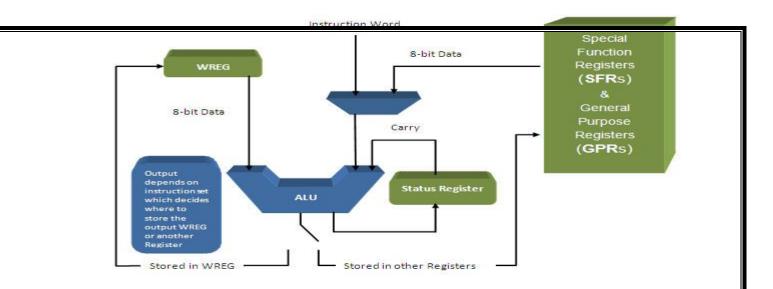

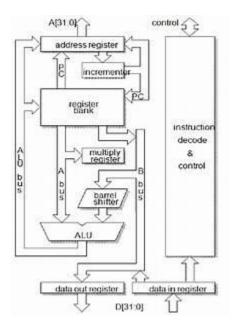

The internal functions of 8086 processor are partitioned logically into two processing units.

The 8086 CPU is divided into two independent functional parts,

## 1. Bus Interface Unit (BIU)

## 2. Execution Unit (EU)

- ✓ The BIU and EU function independently.

- ✓ The BIU interface the 8086 to the outside world. The BIU fetches, reads data from memory and ports, and writes data to memory and I/O ports.

- ✓ EU receives program instruction codes and data from the BIU, executes these instructions and stores the results either in general registers or output them puts all its data through the BIU.

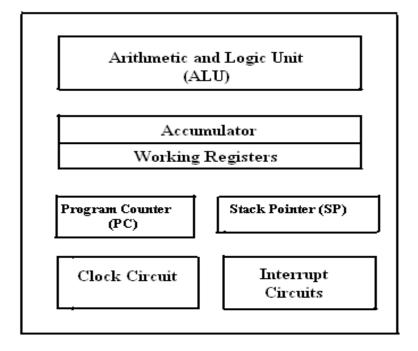

## The BIU contains

1. Segment Registers, 2. Instruction Pointer (IP), 3.Instruction Queue

The EU contains

- 1. ALU

- 2. General purpose registers

- 3. Index registers

- 4. Pointers

- 5. Flag register

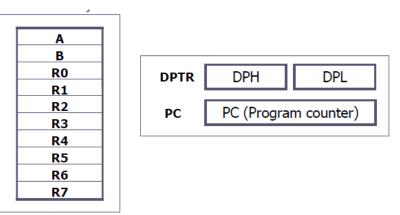

## EC 8691-Microprocessor and Microcontroller General Purpose Registers

All general registers of the 8086 microprocessor can be used for arithmetic and logic operations. The 16

bit general purpose registers are

- 1. Accumulator register (AX)

- 2. Base register (BX)

- 3. Count register (CX)

- 4. Data register (DX)

## (i) Accumulator register (AX)

- $\checkmark$  Accumulator (AX) is a 16 bit register; consists of two 8-bit registers AL and AH.

- $\checkmark$  AL contains the low-order byte of the word, and AH contains the higher order byte.

- ✓ Accumulator can be used for Input/ Output (I/O) operations and string manipulation.

## (ii) Base register (BX)

- ✓ Base register (BX) is a 16 bit register; consist of two 8-bit registers BL and BH.

- $\checkmark$  BL consist the lower order byte of the word, and BH contains the higher order byte.

- ✓ BX register contains a data pointer used for based, based indexed or register indirect addressing.

## (iii) Count register (CX)

- ✓ Counter register (CX) is a 16 bit register; consists of two 8-bit registers CL and CH.

- ✓ CL register contain the low order byte of the word, and CH contains the high order byte.

- $\checkmark$  Count register can be used as a counter in string manipulation and shift/ rotate instructions.

## (iv)Data register (DX)

- $\checkmark$  Data register (CX) is a 16 bit register; consists of two 8-bit registers DL and DH.

- $\checkmark$  DL register contain the low order byte of the word, and DH contains the high order byte.

- $\checkmark$  Data register can be used as a port number in I/O operations.

- ✓ In integer 32-bit multiply and divide instruction the DX register contains higher order word of the initial or resulting number.

## **Segment Registers**

There are four different 64 KB segments for instructions, stack, data and extra data.

The segment registers are:

- 1. Code segment (CS)

- 2. Stack segment (SS)

- 3. Data segment (DS)

- 4. Extra segment (ES)

3

#### Unit-1

## (i) Code segment (CS)

- ✓ Code segment is a 16-bit register containing address of 64 KB segment with processor instructions.

- $\checkmark$  The processor uses CS register for all accesses to instructions referenced by instruction pointer (IP).

- $\checkmark$  CS register cannot be changed directly.

- ✓ The CS register is automatically updated during FAR JUMP, FAR CALL and FAR RET instructions

## (ii) Stack segment (SS)

- ✓ Stack segment is a 16-bit register containing address of 64KB segment with program stack.

- ✓ By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers are located in the stack segment.

- ✓ SS register can be changed directly using POP instruction.

## (iii) Data segment (DS)

- ✓ Data segment is a 16-bit register containing address of 64KB segment with program data.

- ✓ By default, the processor assumes that all data referenced by general registers (AX, BX, CX, and DX) and index register (SI, DI) is located in the data segment.

- ✓ DS register can be changed directly using POP and LDS instructions.

## (iv) Extra segment (ES)

- ✓ Extra segment is a 16-bit register containing address of 64KB segment, usually with program data.

- ✓ By default, the processor assumes that the DI register references the ES segment in string 'manipulation instructions.

- ✓ ES register can be changed directly using POP and LES instructions.

- ✓ It is possible to change default segments used by general and index registers by prefixing instructions with a CS, SS, DS or ES prefix.

## **Pointer Registers**

## (i) Stack Pointer (SP)

Stack pointer is a 16-bit register pointing to program stack.

## (ii) Base Pointer (BP)

- ✓ Base pointer is a 16-bit register pointing to data in the stack segment.

- ✓ BP register is usually used for based, based indexed or register indirect addressing.

## EC 8691-Microprocessor and Microcontroller Index Registers: (i) Source Index (SI)

- ✓ Source index is a 16-bit register.

- ✓ SI is used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions.

## (ii) Destination Index (DI)

- ✓ Destination index is a 16-bit register.

- ✓ DI is used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions.

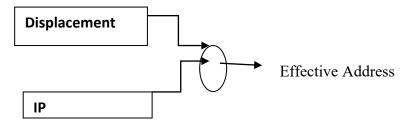

## **Instruction Pointer (IP)**

- ✓ Instruction pointer is a 16-bit register. The operation is same as the program counter.

- $\checkmark$  The IP register is updated by the BIU to point to the address of the next instruction.

- ✓ Programs do not have direct access to the IP, but during execution of a program the IP can be modified or saved and restored from the stack.

## **Flag register**

Flag register is a 16-bit register containing nine 1-bit flags:

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5 | 4  | 3 | 2  | 1 | 0  |

|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|----|

|    |    |    |    | OF | DF | IF | TF | SF | ZF |   | AF |   | PF |   | CF |

Six status or condition flags (OF, SF, ZF, AF, PF, CF)

Three control flags (TF, DF, IF)

- Overflow Flag (OF) It is set if an overflow occurs, i.e., a result is out of range.

- Sign Flag (SF) It is set if the most significant bit of the result is set.

- Zero Flag (ZF) It is set if the result is zero.

- Auxiliary carry Flag (AF) It is set if there is a carry out of bit 3 during addition or borrow by bit 3 during subtraction. This flag is used exclusively for BCD arithmetic.

- Parity Flag (PF) It is set to 1 if the low-order 8-bits of the result contain an even number of 1s.

- Carry Flag (CF) It is set if carry from or borrow to the most significant bit during last result calculation.

- Trap Flag (TF) if set, a trap is executed after each instruction.

- Direction Flag (DF) Used by string manipulation instructions. If set then string manipulation instructions will auto- decrement index registers. If cleared then the index registers will be auto-incremented.

- Interrupt-enable Flag (IF) Setting this bit enables maskable interrupts.

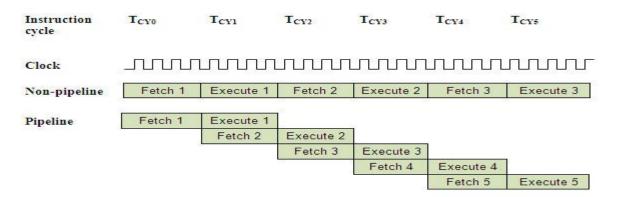

# ✓ <u>It is being done to speedup program execution by overlapping instruction fetch and execution.</u> This mechanism is known as PIPELINING.

- ✓ If the queue is full, the BIU does not perform any bus cycle. If the BIU is not full and can store atleast 2 bytes and EU does not request it to access memory, the BIU may pre-fetch instructions.

- ✓ If the BIU is interrupted by the EU for memory access while pre-fetching, the BIU first completes fetching and then services the EU. In case of JMP instruction, the BIU will reset the queue and .begin refilling after passing the new instruction to the EU.

## ALU: Arithmetic and Logic Unit

ALU is a 16 bit register. It can add, subtract, increment, decrement, complement, shift numbers and performs AND, OR, XOR operations.

#### **Control unit:**

Generates timing and control signals to perform the internal operations of the microprocessor.

## 3. The 8086 Addressing Modes

# AUQ: What are the addressing modes in 8086? Explain with example.(Dec-2006,07,08,10,11, May2006,07,08,09,11,15, May 2016, Dec 2016)

## Addressing modes in 8086:

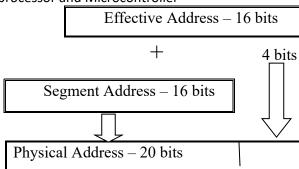

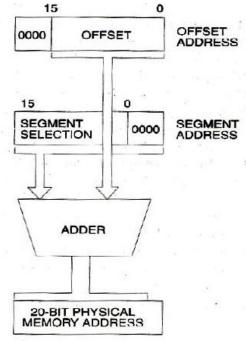

The 8086 memory addresses are calculated by adding the segment register contents to an offset address. The offset address calculation depends on the addressing mode being used. The total number of address lines in the 8086 is 20 whereas the segment registers are 16 bits. The actual address in memory (effective address) is calculated as per the following steps.

- The segment register contents are multiplied by 10H, thus, shifting the contents left by 4 bits. This results in the starting address of the segment in memory.

- The offset address is calculated. The offset address is basically the offset of the actual memory location from the starting location of the segment. The calculation of this offset value depends on the addressing mode being used.

- The offset address is added to the starting address of the segment to get the effective address, i.e. the actual memory address.

Unit-1

Suppose a segment register contents are xyzwH, and the offset value calculated is abcdH, then:

- Starting address of the segment

- Offset address

- Effective address

The addressing modes specify the location of the operand and also how its location may be determined. The following addressing modes are supported in the 8086.

- Register Addressing Mode

- Immediate Addressing Mode

- Direct Memory Addressing Mode

- Register Indirect Addressing Mode

- Base plus Index Register Addressing Mode

- Register Relative Addressing Mode

- Base plus Index Register Relative Addressing Mode

- String Addressing Mode

## **Register Addressing Mode**

When both destination and source operands reside in registers, the addressing mode is known as register addressing mode. Following are the examples:

➢ MOVAX,BX

Move the contents of BX register to AX register. The contents of BX register remain unchanged.

≻ AND AL, BL

AND the contents of AL register with the contents of BL register and place the resultant contents in AL register.

## **Immediate Addressing Mode**

When one of the operands is part of the instruction, the addressing mode is known as immediate addressing mode. Examples are given below

7

Unit-1

• MOV CX, 2346H

Copy into CX the 16-bit data 2346H.

SUB AL, 24H

Subtract 24H from the contents of AL register and put the result in AL register.

## **Direct Memory Addressing Mode**

In this mode, the 16-bit offset address is part of the instruction as displacement field. It is stored as 16-bit unsigned or 8-bit sign-extended number.

≻ MOV (4625H), Dl

Copy the contents of DL register into memory locations calculated from Data Segment register and offset 4625H.

≻ OR AL, (3030H)

OR the contents of AL register with the contents of memory location calculated from DS register and offset 3030H.

#### **Register Indirect Addressing Mode**

In this addressing mode, the offset address is specified through pointer register or index register.

For index register, the SI (Source Index) register or DI (Destination Index) register may be used, whereas for pointer register, BX (Base Register) register or BP (Base Pointer) register may be used. Following are some examples of the application of the register indirect addressing mode.

## ≻ MOV AL, (BP)

Copy into AL register the contents of memory location, whose address is calculated using offset as contents of BP register and the contents of DS register.

#### **Base plus Index Register Addressing Mode**

In this mode, both base register (BP or BX) and index register (SI or DI) are used to indirectly address the memory location. An example is given below.

$\succ$  MOV (BX + DI), AL

Copy the contents of AL register into memory location whose address is calculated using the contents of DS (Data Segment), BX (Base Register) and DI (Destination Index) registers.

## **Register Relative Addressing Mode**

This mode is similar to base plus index addressing mode. In this mode, the offset is calculated using either a base register (BP, BX) or an index register (SI, DI) and the displacement specified as an 8-bit or a 16-bit number, as part of the instruction.

EC 8691-Microprocessor and Microcontroller ➤ MOV AX, (DI + 06)

Copy to AL the contents of memory location whose address is calculated using DS (Data Segment), DI (Destination Index) register with displacement of 06, and copy to AH the contents of the next higher memory location.

## Base plus Index Register Relative Addressing Mode

This addressing mode is basically the combination of base plus index register addressing mode and register relative addressing mode. To find the address of the operand in memory, a base register (BP or BX), an index register (DI or SI) and the displacement which is specified in instruction is used along with the data segment register. For example:

➤ MOV (BX + DI + 2), CL

Copy the contents of the CL register to the memory location whose address is calculated using DS (Data Segment), BX (Base Register) and DI (Destination Index) registers and 02 as displacement.

#### **String Addressing Mode**

In this addressing mode, the string instruction uses index registers implicitly to access memory.

Example: MOVSB

Copy the byte from the source string location determined by DS and SI to the destination string location determined by ES and DI.

- > The addressing modes for **branch related instructions** are

- Intrasegment direct (within the same segment)

- Intrasegment Indirect

- > Intersegment Direct (Control transfer to different segment)

- Intersegment Indirect

#### Intrasegment direct (within the same segment)

If the displacement is 8 bit long, it is called short jump SJMP

If the displacement is 16 bit long, it is called Long jump LJMP.

## For example CALL NEAR

A NEAR JMP is a jump where destination location is in the same code segment. In this case only IP

EC 8691-Microprocessor and Microcontroller is changed.

#### **Intrasegment Indirect**

The content of register or memory is accessed using any of the above data related addressing mode except immediate mode.

#### Intersegment Direct (control transfer is in different segment)

The purpose of the addressing mode is to provide a means of branching from one code segment to another .Replaces the content of IP with the part of the instruction and the contents of the CS with another part of instruction.

#### **Example: FAR CALL**

A FAR JMP is a jump where destination location is from a different segment. In this case both IP and CS are changed as specified in the destination.

#### **Intersegment Indirect**

The content of memory block containing 4 bytes.ie IP (LSB),IP(MSB),CS (LSB),and CS(MSB) sequentially .The starting address of the memory block may be referred using any of the addressing mode except immediate mode.

#### 4. The instruction set of 8086.

Explain the instruction set of 8086 microprocessor.

Give three examples for the following 8086 microprocessor instructions: String Instructions,

Process Control Instruction, Program Execution Transfer Instructions and Bit manipulation Instructions. (May 2010)(June 2016)

Explain the data transfer, arithmetic and branch instructions with examples. (June 2016)

Intel 8086 has approximately 117 instructions. These instructions are used to transfer data between registers, register to memory, memory to register or register to I/O ports and other instructions are used for data manipulation.

But in Intel 8086 operations between memory to memory is not permitted. These instructions are classified in to six-groups as follows.

- 1. Data Transfer Instructions

- 2. Arithmetic Instructions

- 3. Bit Manipulation Instructions

- 4. String Instructions

- 5. Program Execution Transfer Instructions

- 6. Processor Control Instructions

#### EC 8691-Microprocessor and Microcontroller **Data Transfer Instructions**

General-Purpose

|                           |       | mpueouput                      |  |  |  |  |  |  |

|---------------------------|-------|--------------------------------|--|--|--|--|--|--|

|                           | IN    | Input byte or word             |  |  |  |  |  |  |

|                           | OUT   | Output byte or word            |  |  |  |  |  |  |

|                           | Addr  | Address Object and Stack Frame |  |  |  |  |  |  |

|                           | LEA   | Load effective address         |  |  |  |  |  |  |

|                           | LDS   | Load pointer using DS          |  |  |  |  |  |  |

| eneral-Purpose            | LES   | Load pointer using ES          |  |  |  |  |  |  |

| -                         | ENTER | Build stack frame              |  |  |  |  |  |  |

| Move byte or word         | LEAVE | Tear down stack frame          |  |  |  |  |  |  |

| Push word onto stack      |       |                                |  |  |  |  |  |  |

| Pop word off stack        |       | Flag Transfer                  |  |  |  |  |  |  |

| Push registers onto stack | LAHF  | Load AH register from flags    |  |  |  |  |  |  |

| Pop registers off stack   | SAHF  | Store AH register in flags     |  |  |  |  |  |  |

| Exchange byte or word     | PUSHF | Push flags from stack          |  |  |  |  |  |  |

| Translate byte            | POPF  | Pop flags off stack            |  |  |  |  |  |  |

|                           |       | •                              |  |  |  |  |  |  |

Input/Output

#### Unit-1

#### **1. MOV**

MOV

PUSH

POP

PUSHA

POPA

XCHG

XLAT

#### **MOV** destination, source

This (Move) instruction transfers a byte or a word from the source operand to the destination operand.  $(DEST) \leftarrow (SRC), DEST = Destination, SRC = Source$

#### **Example:**

MOV AX, BX

MOVAX, 2150H

MOV AL, [1135]

MOV [4186], AL

MOV SS, DX

MOV [BX], DS

## 2. PUSH

#### **PUSH Source**

This instruction decrements SP (stack pointer) by 2 and then transfers a word from the source operand to the top of the stack now pointed to by stack pointer.

$(SP) \leftarrow (SP)-2$

$((SP) + 1: (SP)) \leftarrow (SRC)$

#### **Example:**

. . . 11

PUSH BX

#### 3. POP

#### **POP** destination

This instruction transfers the word at the current top of stack (pointed to by SP) to the destination operand and then increments SP by 2, pointing to the new top of the stack.

$(DEST) \leftarrow ((SP) + 1:(SP))$

$(SP) \leftarrow (SP) + 2$

**Example:**

POP DX

POP DS

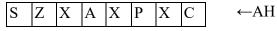

## 4. LAHF

Load Register AH from Flags

This instruction copies Sign flag(S), Zero flag (Z), Auxiliary flag (AC). Parity flag (P) and Carry flag (C) of 8085 into bits 7, 6, 4, 2 and 0 respectively, of register AH. The content of bits 5, 3 and 1 is undefined.

$AH \leftarrow \qquad S \quad Z \quad X \quad A \quad X \quad P \quad X \quad C$

## 5. SAHF

Store Register AH into Flags

This instruction transfers bits 7, 6, 4, 2 and 0 from register AH into S, Z, AC, P and C flags respectively, thereby replacing the previous values.

## 6. XCHG

#### **XCHG destination, source**

This (Exchange) instruction switches the contents of the source and destination operands.

$(\text{Temp}) \leftarrow (\text{DEST})$

$(DEST) \leftarrow (SRC)$

$(SRC) \leftarrow (Temp)$

## **Example:**

XCHG AX, BX

XCHG BL, AL

#### 7. XLAT

## XLAT table

- This (Translate) instruction replaces a byte in the AL register with a byte from a 256-byte, user-coded translation table.

- XLAT is useful for translating characters from one code to another like ASCII to EBCDIC. Register BX is the starting point of the table. The byte in AL is used as an index into the table and is replaced by the byte at the offset in the table corresponding to AL's binary value.

$AL \leftarrow ((BX) + (AL))$

#### Example :

```

XLAT ASCII_TAB

```

XLAT Table\_3

#### 8. LEA

#### LEA destination, source

This (Load Effective Address) instruction transfers the offset of the source operand (memory) to the destination operand (16-bit general register).

$(REG) \leftarrow EA$

#### Example :

LEA BX, [BP] [DI] LEA SI, [BX + 02AF H]

#### 9. LDS

#### LDS destination, source

This (Load pointer using DS) instruction transfers a 32-bit pointer variable from the source operand (memory operand) to the destination operand and register DS.

$(REG) \leftarrow (EA)$

$(DS \leftarrow (EA+2))$

## Example:

LDS SI, [6AC1H]

#### 10. LES

#### LES destination, source

This (Load pointer using ES) instruction transfers a 32-bit pointer variable from the source operand (memory operand) to the destination operand and register ES.

$(REG) \leftarrow (EA)$

$(ES) \leftarrow (EA+2)$

LES DI, [BX]

## 11. IN

## IN accumulator, port

This (Input) instruction transfers a byte or a word from an input port to the accumulator (AL or AX).

$(DEST) \leftarrow (SRC)$

## Example:

IN AX, DX

IN AL, 062H

## 12. OUT

## OUT port, accumulator

This (Output) instruction transfers a byte or a word from the accumulator (AL or AX) to an output port.

$(DEST) \leftarrow (SRC)$

## Example:

OUT DX, AL

OUT 31, AX

## **Arithmetic Instructions**

|     | Addition                          |                |                                 |  |  |

|-----|-----------------------------------|----------------|---------------------------------|--|--|

| ADD | ADD Add byte or word              |                |                                 |  |  |

| ADC | Add byte or word with carry       |                |                                 |  |  |

| INC | Increment byte or word by 1       |                |                                 |  |  |

| AAA | ASCII adjust for addition         |                |                                 |  |  |

| DAA | Decimal adjust for addition       | Multiplication |                                 |  |  |

|     | Subtraction                       | MUL            | Multiply byte or word unsigned  |  |  |

|     |                                   | IMUL           | Integer multiply byte or word   |  |  |

| SUB | Subtract byte or word             | AAM            | ASCII adjust for multiplication |  |  |

| SBB | Subtract byte or word with borrow | Division       |                                 |  |  |

| DEC | Decrement byte or word by 1       | DIV            | Divide byte or word unsigned    |  |  |

| NEG | Negate byte or word               | IDIV           | Integer divide byte or word     |  |  |

| CMP | Compare byte or word              | AAD            | ASCII adjust for division       |  |  |

| AAS | ASCII adjust for subtraction      | CBW            | Convert byte to word            |  |  |

| DAS | Decimal adjust for subtraction    | CWD            | Convert word to double-word     |  |  |

1. ADD

## ADD destination, source

This (Add) instruction adds the two operands (byte or word) and stores the result in destination operand.

```

(DEST) \leftarrow (DEST) + (SRC)

```

Example:

ADD CX, DX

ADD AX, 1257 H

ADDBX, [CX]

## **2. ADC**

## ADC destination, source

This (Add with carry) instruction adds the two operands and adds one if carry flag (CF) is set and stores the result in destination operand.

$(DEST) \leftarrow (DEST) + (SRC) + 1$

## Example:

ADC AX, BX

ADC AL, 8

ADC CX, [BX]

## 3. SUB

## SUB destination, source

This (Subtract) instruction subtracts the source operand from the destination operand and the result is stored in destination operand.

$(DEST) \leftarrow (DEST) - (SRC)$

## Example:

SUB AX, 6541 H

SUB BX, AX

SUB SI, 5780 H

## 4. SBB

## SBB destination, source

This (**Subtract with Borrow**) instruction subtracts the source from the destination and subtracts 1 if carry flag (CF) is set. The result is stored in destination operand.

$(DEST) \leftarrow (DEST) - (SRC) - 1$

## Example:

EC 8691-Microprocessor and Microcontroller SBB BX, CX

SBB AX, 2

## **5.** CMP

## CMP destination, source

This (Compare) instruction subtracts the source from the destination, but does not store the result.

(DEST) - (SRC)

## Example:

CMP AX, 18

CMP BX, CX

## 6. INC

## **INC destination**

This (Increment) instruction adds 1 to the destination operand (byte or word).

$(DEST) \leftarrow (DEST) + 1$

## Example:

INC BL

INC CX

## **7. DEC**

**DEC** destination

This (Decrement) instruction subtracts 1 from the destination operand.

$(DEST) \leftarrow (DEST)-1$

## **Example:**

DEC BL

DEC AX

## 8. NEG

## **NEG** destination

This (Negate) instruction subtracts the destination operand from 0 and stores the result in destination. This forms the 2's complement of the number.

$(DEST) \leftarrow 0 - (DEST)$

## **Example:** NEG AX

NEG CL

This (Decimal Adjust for Addition) instruction converts the binary result of an ADD or ADC instruction in AL to packed BCD format.

If the auxiliary carry flag is set or the low 4 bits of AL are greater than 9, then 06 H is added to AL. If the carry flag is set or the high 4 bits of AL are greater than 9, then 60 H is added to the AL.

## 10. DAS

This (Decimal Adjust for Subtraction) instruction converts the binary result of a SUB or SBB instruction in AL to packed BCD format.

## **11.AAA**

This (ASCII Adjust for Addition) instruction adjusts the binary result of ADD or ADC instruction.

If bits 0-3 of AL contain a value greater than 9, or if the auxiliary carry flag (AF) is set, the CPU adds 06 to AL and adds 1 to AH. The bits 4-7 of AL are set to zero.

$(AL) \leftarrow (AL) + 6$  $(AH) \leftarrow (AH) + 1$

$(AF) \leftarrow 1$

## Example:

AAA

Before execution

AH AL

00 0B

After execution

AH AL

01 01

## **12. AAS**

This (ASCII Adjust for Subtraction) instruction adjusts the binary result of a SUB or SBB instruction.

```

If D_3 - D_0 of AL > 9,

(AL) \leftarrow (AL) - 6

(AH) \leftarrow (AH) - 1

(AF) \leftarrow 1

```

## 13.MUL

MUL source

- This (Multiply) instruction multiply AL or AX register by register or memory location contents.

- Both operands are unsigned numbers.

- If the source is a byte (8 bit), then it is multiplied by register AL and the result is stored in AH and AL.

- If the source operand is a word (16 bit), then it is multiplied by register AX and the result is stored in AX and DX registers.

If 8 bit data,  $(AX) \leftarrow (AL) \times (SRC)$

If 16 bit data, (AX), (DX)  $\leftarrow$  (AX)  $\times$  (SRC)

#### Example:

MUL25

MUL CX .

MULBL

#### **14.IMUL**

#### **IMUL Source**

This (Integer Multiply) instruction performs a signed multiplication of the source operand and the accumulator.

If 8 bit data,  $(AX) \leftarrow (AL) \times (SRC)$ If 16 bit data,  $(AX), (DX) \leftarrow (AX) \times (SRC)$

#### **Example:**

IMUL 250

IMUL BL

#### 15. AAM

This (ASCII Adjust for Multiplication) instruction adjusts the binary result of a MUL instruction. AL is divided by 10(0AH) and quotient is stored in AH. The remainder is stored in AL.

$(AH) \leftarrow (AL/OAH)$

$(AL) \leftarrow Remainder$

#### 16. DIV

#### **DIV Source**

- This (Division) instruction performs an unsigned division of the accumulator by the source operand.

- It allows a 16 bit unsigned number to be divided by an 8 bit unsigned number, or a 32 bit unsigned number to be divided by a 16 bit unsigned number.

- If byte (8-bit) operation is performed, the 8 bit quotient is stored to AL and 8 bit remainder is stored to AH register.

• If the source operand is a word (16 bit), the 16 bit quotient is stored in AX and the remainder is stored in DX register.

For 8 bit data, AX / source

$(AL) \leftarrow Quotient$

$(AH) \leftarrow Remainder$

For 16 bit data, AX, DX / Source

$(AX) \leftarrow Quotient$

$(DX) \leftarrow Remainder$

#### **Example:**

DIV CX

DIV 321

#### 17.IDIV

#### **IDIV** source

This (Integer Division) instruction performs a signed division of the accumulator by the source operand.

For 8 bit data, AX / Source

$(AL) \leftarrow Quotient$

$(AH) \leftarrow Remainder$

For 16 bit data, AX, DX/Source

$(AX) \leftarrow Quotient$

$(DX) \leftarrow Remainder$

#### **Example:**

IDIV CL

IDIVAX

#### 18. AAD

This (ASCII Adjust for Division) instruction adjusts the unpacked BCD dividend in AX before a division operation. AH is multiplied by 10(0AH) and added to AL. AH is set to zero.

$(AL) \leftarrow (AH \times 0AH) + (AL)$

$(\mathrm{AH}) \! \leftarrow \! 0$

#### **19. CBW**

This (Convert Byte to Word) instruction converts a byte to a word. It extends the sign of the byte in register AL through register AH.

EC 8691-Microprocessor and Microcontroller This instruction can be used for 16 bit IMUL or IDIV instruction.

Unit-1

## **Example:**

CBW

| Before execution | After ex | xecution |  |

|------------------|----------|----------|--|

| AL               | AH       | AL       |  |

| 85               | FF       | 85       |  |

| AL               | AH       | AL       |  |

| 41               | 00       | 41       |  |

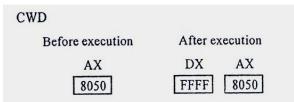

#### 20. CWD

This (Convert Word to Double word) instruction converts a word to a double word. It extends the sign of the word in register AX through register DX.

If AX < 8000 H, then DX = 0000 H

If AX > 8000 H, then DX = FFFFH

## **Example:**

## **Bit Manipulation Instructions**

|                          | Logicals                                   |  |  |  |  |  |  |

|--------------------------|--------------------------------------------|--|--|--|--|--|--|

| NOT                      | "Not" byte or word                         |  |  |  |  |  |  |

| AND                      | "And" byte or word                         |  |  |  |  |  |  |

| OR                       | "Inclusive or" byte or word                |  |  |  |  |  |  |

| XOR                      | XOR "Exclusive or" byte or word            |  |  |  |  |  |  |

| TEST "Test" byte or word |                                            |  |  |  |  |  |  |

| Shifts                   |                                            |  |  |  |  |  |  |

| SHL/SAL                  | Shift logical/arithmetic left byte or word |  |  |  |  |  |  |

| SHR                      | Shift logical right byte or word           |  |  |  |  |  |  |

| SAR                      | Shift arithmetic right byte or word        |  |  |  |  |  |  |

|                          | Rotates                                    |  |  |  |  |  |  |

| ROL                      | Rotate left byte or word                   |  |  |  |  |  |  |

| ROR                      | Rotate right byte or word                  |  |  |  |  |  |  |

| RCL                      | Rotate through carry left byte or word     |  |  |  |  |  |  |

| RCR                      | Rotate through carry right byte or word    |  |  |  |  |  |  |

- (i) Logical Instructions : AND, OR, XOR, NOT, TEST

- (ii) Shift Instructions : SHL, SAL, SHR, SAR

- (iii) Rotate Instructions : ROL, ROR, RCL, RCR

#### 1. AND

#### AND destination, source

This (AND) instruction performs the logical "AND" of the source operand with the destination operand and the result is stored in destination.

$(DEST) \leftarrow (DEST)$  "AND" (SRC)

#### **Example:**

AND BL, CL

AND AL, 0011 1100 B

#### 2. OR

#### **OR** destination, source

This **(OR)** instruction performs the logical "OR" of the source operand with the destination operand and the result is stored in destination.

$(DEST) \leftarrow (DEST) "OR" (SRC)$

#### **Example:**

OR AX, BX

OR AL, 0FH

#### 3. XOR

#### XOR destination, source

This (Exclusive OR) instruction performs the logical "XOR" of the two operands and the result is stored in destination operand.

$(DEST) \leftarrow (DEST) "XOR"(SRC)$

#### **4. NOT**

#### **NOT** destination

This (NOT) instruction inverts the bits (forms the l's complement) of the byte or word.

(DEST)  $\leftarrow$  1 's complement of (DEST)

#### **Example:**

NOT AX

## 5. TEST

**TEST destination, source**

#### Unit-1

This (TEST) instruction performs the logical "AND" of the two operands and updates the flags but does not store the result.

(DEST) "AND" (SRC)

## **Example:**

TEST AL, 15 H

TEST SI, DI

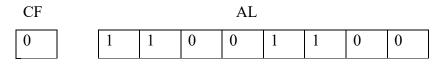

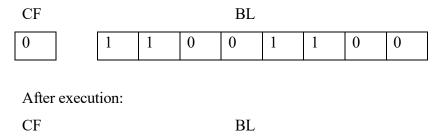

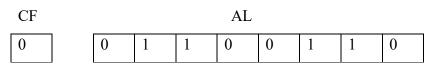

## 6. SHL

## SHL destination, count

This (Shift Logical Left) instruction performs the shift operation. The number of bits to be shifted is represented by a variable count, either 1 or the number contained in the CL register.

## Example

SHL AL, 1

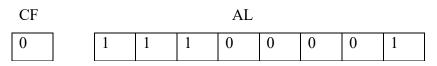

Before execution:

After execution:

| CF | AL |   |   |   |   |   |   |   |

|----|----|---|---|---|---|---|---|---|

| 1  | 1  | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

## 7. SAL

## SAL destination, count

SAL (Shift Arithmetic Left) and SHL (Shift Logical Left) instructions perform the same operation and are physically the same instruction.

## Example

SAL AL, CL

SAL AL, 1

## 8. SHR

SHR destination, count

```

Unit-1

```

This (Shift Logical Right) instruction shifts the bits in the destination operand to the right by the number of bits specified by the count operand, either 1 or the number contained in the CL register.

#### Example

SHR BL, 1

SHR BL, CL

The SHR instruction may be used to divide a number by 2. For example, we can divide 32 by 2,

| MOV BL, 32 | ; | 0010 | 0000 | (32) |

|------------|---|------|------|------|

| SHR BL, 1  | ; | 0001 | 0000 | (16) |

| SHR BL, 1  | ; | 0000 | 1000 | (8)  |

| SHR BL, 1  | ; | 0000 | 0100 | (4)  |

| SHR BL, I  | ; | 0000 | 0010 | (2)  |

|            |   |      |      |      |

## 9. SAR

## SAR destination, count

This (Shift Arithmetic Right) instruction shifts the bits in the destination operand to the right by the number of bits specified in the count operand. Bits equal to the original high-order (sign) bits are shifted in on the left, thereby preserving the sign of the original value.

## Example :

SAR BL, 1

Before execution:

| EC 8691-N | Microp | rocesso | or and I | Microco | ontrolle | er |   |   |   | Unit-1 |  |

|-----------|--------|---------|----------|---------|----------|----|---|---|---|--------|--|

| 0         |        | 1       | 1        | 1       | 0        | 0  | 1 | 1 | 0 |        |  |

#### 10. ROL

#### **ROL** destination, count

This (Rotate Left) instruction rotates the bits in the byte/word destination operand to the left by the number of bits specified in the count operand.

## **Example:**

ROL AL, 1

Before execution:

| CF | AL |   |   |   |   |   |   |   |  |

|----|----|---|---|---|---|---|---|---|--|

| 0  | 1  | 1 | 0 | 0 | 1 | 1 | 0 | 0 |  |

After execution:

| CF |   |   |   | AL |   |   |   |   |

|----|---|---|---|----|---|---|---|---|

| 1  | 1 | 0 | 0 | 1  | 1 | 0 | 0 | 1 |

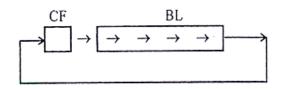

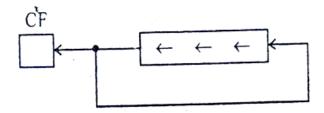

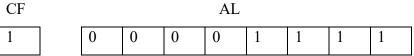

## 11. ROR

#### **ROR** destination, count

This (Rotate Right) instruction rotates the bits in the byte/word destination operand to the right by the number of bits specified in the count operand.

## Example:

ROR AL, 1

Before execution:

After execution:

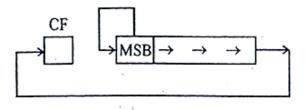

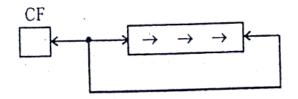

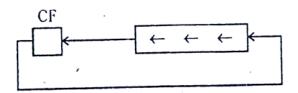

## 12. RCL

#### **RCL** destination, count

This (Rotate through Carry Left) instruction rotates the contents left through carry by the specified number of bits in count operand.

## **Example:**

RCL AL, 1

Before execution:

CF

After execution:

| CF |   |   |   | AL |   |   |   |   |

|----|---|---|---|----|---|---|---|---|

| 0  | 0 | 0 | 0 | 1  | 1 | 1 | 1 | 1 |

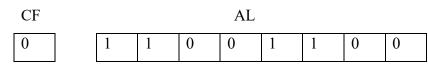

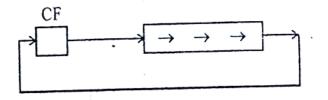

## **13.RCR**

## **RCR** destination, count

This (Rotate through Carry Right) instruction rotates the contents right through carry by the specified number of bits in the count operand.

Unit-1

## Example:

RCR AL, 1

Before execution:

CF

AL

1

1

0

0

0

1

0

After execution:

## **String Instructions**

| REP         | Repeat                          |

|-------------|---------------------------------|

| REPE/REPZ   | Repeat while equal/zero         |

| REPNE/REPNZ | Repeat while not equal/not zero |

| MOVSB/MOVSW | Move byte string/word string    |

| MOVS        | Move byte or word string        |

| INS         | Input byte or word string       |

| OUTS        | Output byte or word string      |

| CMPS        | Compare byte or word string     |

| SCAS        | Scan byte or word string        |

| LODS        | Load byte or word string        |

| STOS        | Store byte or word string       |

## 1. REP

Unit-1

## **Example:**

REP MOVS CL, AL

The other Repeat instructions are:

- REPE Repeat while Equal

- REPZ Repeat while zero

- REPNE Repeat while Not Equal

- REPNZ Repeat while Not Zero

The above instructions are used with the CMPS and SCAS instructions.

#### **Example:**

REPE CMPS destination, source

REPNE SCAS destination

#### 2.MOVS

#### MOVS destination - string, source-string

This (Move String) instruction transfers a byte/word from the source string (addressed by SI) to the destination string (addressed by DI) and updates SI and DI to point to the next string element.

$(DEST) \leftarrow (SRC)$

## **Example:**

MOVS Buffer 1, Buffer 2

## 3. CMPS

## CMPS destination-string, source-string

This (Compare String) instruction subtracts the destination byte/word (addressed by DI) from the source byte/word (addressed by SI). It affects the flags but does not affect the operands. -.

#### Example:

CMPS Buffer 1, Buffer 2

## 4. SCAS

SCAS destination-string

• This (Scan String) instruction subtracts the destination string element (addressed by DI) from the

contents of AL or AX and updates the flags.

- 'The contents of destination string or accumulator are not altered.

- After each operation, DI is updated to point to the next string element

## **Example:**

SCAS Buffer

## 5. LODS

## LODS source-string

This (Load String) instruction transfers the byte/word string element addressed by SI to register AL or AX and updates SI to point to the next element in the string.

(DEST)←(SRC)

## Example:

LODSB name

LODSW name

## 6. STOS

## **STOS destination - string**

This (Store String) instruction transfers a byte/word from register AL or AX to the string element addressed by DI and updates DI to point to the next location in the string.

$(DEST) \leftarrow (SRC)$

Example: STOS display

## **Program Transfer Instructions**

Unconditional instructions : CALL, RET, JMP

Conditional instructions : JC, JZ, JA

Iteration control instructions: LOOP, JCXZInterrupt instructions: INT, INTO, IRET

## 1. CALL

## • CALL procedure - name

- This (CALL) instruction is used to transfer execution to a subprogram or procedure.

- RET (return) instruction is used to go back to the main program.

- There are two basic types of CALL : NEAR and FAR

## Intra-Segment CALL:

- A NEAR-CALL is a call to a procedure which is in the same code segment as the CALL instruction.

- When 8086 executes a NEAR-CALL instruction, it decrements the stack pointer (SP) by 2 and copies

the offset of the next instruction after the CALL on the stack.

- It loads IP with the offset of the first instruction of the procedure in same segment.

- This NEAR-CALL is known as Intra-segment CALL.

## **Inter-Segment CALL:**

- A FAR-CALL is a call to a procedure which is in a different segment from that which contains the CALL instruction.

- When 8086 executes a FAR-CALL, it decrements the SP by 2 and copies the contents of the CS register to the stack.

- It then decrements SP by 2 again and copies the offset of the instruction after the CALL to the stack.

- Finally it loads CS with the segment base of the segment which contains the procedure and IP with the offset of the first instruction of the procedure in that segment.

- This FAR-CALL is known as Inter-segment CALL.

## **Example:**

CALL NEAR

CALL AX

## 2.RET

This **(Return)** instruction will return execution from a procedure to the next instruction after the CALL instruction in the main program.

If intra-segment, IP is popped off the stack; SP = SP+2

If inter-segment, CS is popped off the stack; SP = SP+2

IP is popped off the stack; SP=SP+2

If optional POP value is used, then SP= SP + value.

**Example:**

RET

RET 6

## **3. JMP**

## JMP target

This (Jump) instruction unconditionally transfers control to the target location. The target operand may be obtained from the instruction itself (direct JMP) or from memory or a register referenced by the instruction (indirect JMP).

A NEAR-JMP (Intra-segment) is a jump where destination location is in the same code segment. In this case only IP is changed.

IP = IP + signed displacement

A FAR-JMP (Inter-segment) is a jump where destination location is from a different segment. In this case both IP and CS are changes as specified in the destination.

## Example:

JMPBX

## **Conditional JMP**

| Instruction | Operation                                |

|-------------|------------------------------------------|

| JC          | Jump if carry                            |

| JNC         | Jump if no carry                         |

| JZ          | Jump if Zero                             |

| JNZ         | Jump if not zero                         |

| JS          | Jump if sign or negative                 |

| JNS         | Jump if positive                         |

| JP/JPE      | Jump if parity/parity even               |

| JNP/JPO     | Jump if not parity/odd parity            |

| JO          | Jump if overflow                         |

| JNO         | Jump if no overflow                      |

| JA/JNBE     | Jump if above/not below or equal         |

| JAE/JNB     | Jump if above or equal/not below         |

| JB/JNAE     | Jump if below/not above or equal         |

| JBE/JNA     | Jump if below or equal / not above       |

| JG/JNLE     | Jump if greater/not less than nor equal  |

| JGE/JNL     | Jump if greater or equal/not less than   |

| JL/JNGE     | Jump if less/neither greater nor equal   |

| JLE/JNG     | Jump if less than or equal / not greater |

## 5.LOOP

## LOOP label

This (Loop if CX not zero) instruction decrements CX by 1 and transfers control to the target operand if CX is not zero. Otherwise the instruction following LOOP is executed.

If  $CX \neq 0$ , CX = CX - 1

IP = IP + displacement

If CX=0, then the next sequential instruction is executed.

## **Example:**

LOOP again

## 6. LOOPE/LOOPZ

## LOOPE/LOOPZ label

These (LOOP while Equal/Loop while Zero) are different mnemonics for the same instruction.

If CX≠0, CX=CX-1 and control is transferred '.o the target operand

If CX = 0, then next sequential instruction is executed.

## **Example:**

LOOPE again

## 7. LOOPNE/LOOPNZ

## **LOOPNE Label**

These (LOOP while Not Equal/LOOP while Not Zero) are different mnemonics for the same instruction. CX is decremented by 1 and control is transferred to target operand if CX is not zero and if ZF=0; otherwise the next sequential instruction is executed.

## **Example:**

LOOPNE again

## **8. JCXZ**

## JCXZ Label

This (Jump if CX register Zero) instruction transfers control to the target operand if CX=0. It is useful at the beginning of a loop to bypass the loop if CX=0.

## **Example:**

JCXZ again

## 9. INT

## INT interrupt type (0-255)

This (Interrupt) instruction activates the interrupt procedure specified by the interrupt-type number (0-255). The address of the interrupt pointer is calculated by multiplying the interrupt-type number by 4.

## Example :

INT 7, INT 180

Unit-1

## 11.IRET

This (**Interrupt on Return**) instruction transfers control back to the point of interruption by popping IP, CS and the flags from the stack.

IRET is used to exit any interrupt procedure, whether activated by hardware or software.

## **Processor Control Instructions**

## 1. HLT

This (Halt) instruction will cause the 8086 to stop fetching and executing instructions. The 8086 will enter a halt state. The ways to get the processor out of halt state are with (i) an interrupt signal on the INTR pin. (ii) An interrupt signal on the NMI pin, (iii) a reset signal on the RESET pin.

## 2. WAIT

This (Wait) instruction causes the 8086 to enter the wait state while its test line is not active.

## 3. LOCK

- The LOCK prefix allow 8086 to make sure that another processor does not take control of the system bus while it is in the middle of a critical instruction which uses the system bus.

- The LOCK prefix is put in front of the critical instruction.

- When an instruction with a LOCK prefix executes, the 8086 will assert its bus lock signal output. This signal is connected to an external bus controller device which then prevents any other processor from taking over the system bus.

## 4. ESC

- ✓ This (Escape) instruction provides a mechanism by which other coprocessors may receive their instructions from the 8086 instruction stream and make use of the 8086 addressing modes.

- ✓ The 8086 does a no operation (NOP) for the ESC instruction other than to access a memory operand and place it on the bus.

## **5. NOP**

This (No operation) instruction causes the CPU to do nothing. NOP does not affect any flags.

EC 8691-Microprocessor and Microcontroller **6. Flag operations**

| lear the carry flag (CF)       |

|--------------------------------|

|                                |

| complement the carry flag (CF) |

| et the carry flag (CF)         |

| lear the direction flag (DF)   |

| e                              |

| STD | Set the direction flag (DF)   |

|-----|-------------------------------|

| CLI | Clear the interrupt flag (IF) |

| STI | Set the interrupt flag (IF)   |

|     |                               |

Unit-1

#### 5. Assembler directives

# AUQ: Explain the assembler directives in 8086 Microprocessor. (Dec-2006,11,12, May2007,08,10,11,13, Dec 2016)

• An assembler is a program used to convert an assembly language program into the equivalent machine code modules which may further converted into executable codes.

Some directives such as ORG, EQU, DB, DW, etc which are common in different assemblers were also described. Though a representative set of directives for the 8086 assembler is presented, it is possible that some assemblers have a few additional directives. On the other hand, some of the directives presented here may not be present or may be present in different forms.

#### **Directives for Constant and Variable Definition**

An Intel 8086 assembly program uses different types of constants like binary, decimal, octal and hexadecimal. These can be represented in the program using different suffixes like B (for binary), D (for decimal), O (for octal) and H (for hexadecimal) to the constant. For example:

- 10H is a hexadecimal number (equivalent to decimal 16).

- 270 is an octal number (equivalent to decimal 23).

- 10100B is a binary number.

A number of directives are used to define and store different kinds of constants.

The DB (Define Byte), DW (Define Word), DDW (Define Double Word) are described in Chapter The 8086 assembler uses DD as directive for double word. Some of the 8086 assemblers also provide the following additional directives.

- DQ : Define Quadword

- DT : Define Ten Bytes

In addition, these directives can be used to store strings and arrays. For example:

• NAME DB "NEHA SHIKHA". The ASCII codes of alphanumeric characters specified within double quotes are stored.

• NUM DB 5, 6, 10, 12, 7. The array of five numbers NUM is declared and the numbers 5, 6, 10, 12 and 7 are stored.

The directives DUP and EQU are used to store strings and arrays.

#### DUP

Using the DUP directive, several locations may be initialized and the values may be put in those locations. The format is as follows. Name Type Num DUP (value)

For example: TEMP DB 20 DUP (5)

The above directive defines an array of 20 bytes in memory and each location is initialized to 5. The array is named TEMP.

## EQU

The EQU directive may be used to define a data name with immediate value or another data name. It can also be used to equate a name to a string. For example:

NUMB EQU 20H

NAME EQU "RASHMI"

#### **Program Location Control Directives**

The directives used for program location control in the 8086 assembler are (ORG, EVEN, ALIGN and LABEL.

## ORG

The ORG directive is used to set the location counter to a particular value. For example:

▶ ORG 2375H

The location counter is set to 2375H. If it occurs in data segment, the next data storage will start at 2375H. If it is in code segment, the next instruction will start at 2375H.

#### **EVEN**

Using EVEN directive, the next data item or label is made to start at the even address boundary. The assembler, on encountering EVEN directive, will advance the location counter to even address boundary. For example:

## ➢ EVEN TABLE DW 20 DUP (0)

This statement declares an array named TABLE of 20 words starting from the even address. Each word is initialized to zero.

## EC6504-Microprocessor and Microcontroller ALIGN number

This directive will force the assembler to align the next segment to an address that is divisible by 2,

4, 8 or 16. The unused bytes are filled with 0 for data and NOP instruction for code. For example:

> ALIGN 2

It will force the next segment to the next even address.

#### LENGTH

It is an operator which is used to tell the assembler to determine the number of elements in a data item, such as string or array. For example:

MOV CX, LENGTH ARRAY

This statement will move the length of the array to the CX register.

#### OFFSET

This operator is used to determine through the assembler, the offset of a data item from the start of the segment containing it. For example:

#### ➢ MOV AX, OFFSET FACT

This statement will place in the AX register the offset of the variable FACT from the start of the segment.

#### LABEL

The LABEL directive is used to assign a name to the current value in the location counter. The location counter is used by the assembler to keep track of the current location. The value in the location counter denotes the distance of the current location from the start of the segment.

#### **Segment Declaration Directives**

These directives help in declaring various segments with specific names. The start and the end of segments may also be specified using this directive. The directives for segment declaration include SEGMENT, ENDS, ASSUME, GROUP, CODE, DATA, STACK etc.

#### **SEGMENT and ENDS**

The SEGMENT and ENDS directives signify the start and end of a segment.

INST SEGMENT

ASSUME CS: FNST, DS: DATAW

#### INST ENDS ASSUME

This directive is used to assign logical segment to physical segment at any time. It tells the assembler as to what addresses will be in segment registers at the time of execution. For example:

#### ➢ ASSUME CS: CODE, DS: DATA, SS: STACK

This directive tells the assembler that the CS register will store the address of the segment whose name is CODE, and so on.

#### .CODE (Name)

This code directive is the shortcut used in the definition of code segments. The name is optional and is specified if there is more than one code segment in the program.

#### .DATA and .STACK

Similar to .CODE, the .DATA and .STACK directives are shortcuts in the definition of data segment and stack segment, respectively.

#### GROUP

This directive is used to tell the assembler to group all the segments in one logical group segment. This allows the contents of all the segments to be accessed from the same segment base. For example:

#### PROG GROUP CODE, DATA

The above statement will group the two segments CODE and DATA into one segment named PROG. Each segment must be declared using ASSUME statement as in the following statement.

ASSUME CS: PROG DS: PROG

#### **Procedure and Macro-related Directives**

The directives in this group relate to the declaration of procedures and macros along with the variables contained in them. The directives include PROC, ENDP, PUBLIC, MACRO, ENDM and EXTRN.

#### **PROC and ENDP**

The PROC directive is used to define the procedures. The procedure name is a *must* and it must follow the naming convention of the assembler. Along with the name of the procedure, the field NEAR or FAR also needs to be specified.

The ENDP directive is used to mark the end of the procedure. Some examples are given below.

EC6504-Microprocessor and Microcontroller FUNCT PROC FAR

ENDP

FACT PROC NEAR

ENDP

The first procedure FUNCT is in a segment which is different from where it is called. The second procedure FACT is in the same segment where it is called. All the statements of the procedure are between PROC and ENDP directives.

#### PUBLIC

It is very much possible that a variable is defined in one module, but is used in other modules. In order to facilitate the linking, such variables are declared *public*, using the PUBLIC directive in the module where they are defined. For example:

➢ PUBLIC PX, PY, PZ

#### **MACRO and ENDM**

The MACRO directive is used to define macros in the program. The ENDM directive defines the end of MACRO

#### **Other Directives**

These directives are of general nature, or they relate to more than one group described earlier. The directives described include PTR, PAGE, TITLE, NAME and END.

#### PTR

The PTR is an operator used in instructions to assign a specific type to a variable or a label. The PTR operator can also be used to override the declared type of variable. Following is an example of the use of PTR directive.

ARRAY DW 0125H, 1630H, 9275H ...

In the above array of words, suppose we wish to move a byte from the array, we may then simply insert the PTR operator as follows

#### MOV AL, BYTE PTR ARRAY

37

Unit-1

directive is placed to specify the maximum number of lines on a page and the maximum number of characters in a line to be placed for listing. An example is given below.

▶ PAGE 60, 120

The above example specifies that 60 lines are to be listed on a page with a maximum of 120 characters in each line.

# TITLE

This directive is also used for the listing of the program. The title declared in this directive defines the title of the program and is listed in line 2 of each page of program listing. The maximum number of characters allowed is 60. For example:

> TITLE PROGRAM TO FIND SQUARE ROOT

# NAME

The NAME directive is used to assign a specific name to each module, when the program consists of a number of modules. This helps in understanding the program logic.

# END

This is the last statement of the program and it specifies the end of the program to the assembler. It must be noted that not all of the above directives are used in all programs. User may deploy them depending on the need of the program logic.

# 6. <u>ASSEMBLY LANGUAGE PROGRAMS:</u>

| 6-BIT ADDITION USING 8086 | 2                                                                                                      | 2. 16-BIT SUBTRACTION USING 8086                                                                             |

|---------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| IOV DX,0000               |                                                                                                        | MOV DX,0000                                                                                                  |

| IOV AX,[2000]             |                                                                                                        | MOV AX,[2000]                                                                                                |

| IOV BX,[2002]             |                                                                                                        | MOV BX,[2002]                                                                                                |

| DD AX,BX                  |                                                                                                        | SUB AX,BX                                                                                                    |

| NC L1                     |                                                                                                        | JNC L1                                                                                                       |

| NC DX                     |                                                                                                        | INC DX                                                                                                       |

| IOV[2004],AX              | L1                                                                                                     | MOV[2004],AX                                                                                                 |

| IOV[2006],DX              |                                                                                                        | MOV[2006],DX                                                                                                 |

| LT                        |                                                                                                        | HLT                                                                                                          |

| 1                         | OV DX,0000<br>OV AX,[2000]<br>OV BX,[2002]<br>DD AX,BX<br>NC L1<br>NC DX<br>OV[2004],AX<br>OV[2006],DX | OV DX,0000<br>OV AX,[2000]<br>OV BX,[2002]<br>DD AX,BX<br>NC L1<br>NC DX<br>OV[2004],AX<br>L1<br>OV[2006],DX |

38

EC6504-Microprocessor and Microcontroller 3. 16 BIT MULTIPLICATION USING 8086 MOV DX,0000 MOV SI,2000 MOV AX,SI MOV CX,[2002] MUL CX MOV SI,2100 MOV SI,2100 MOV [SI],AX MOV [2102],DX HLT

# 5. 16 BIT ASCENDING ORDER USING 6. 16-BIT 8086 MOV AX,0000H START MOV CX,0005H MOV DX,0005H MOV SI,2000H LABEL MOV AX,[SI] CMP AX, [SI+2] JC LOOP JNC LOOP XCHG AX, [SI+2] XCHG AX,[SI] LOOP ADD SI,0002 LOOP LOOP LABEL DEC DX DEC DX JNZ START HLT HLT

4. 16 BIT DIVISION USING 8086 MOV DX,0000 MOV SI,2000 MOV AX,SI MOV CX,[2002] DIV CX MOV SI,2100 MOV [SI],AX MOV [SI],AX HLT

Unit-1

6. 16-BIT

DESCENDING

ORDER

USING 8086

MOV AX,0000

MOV AX,0005

MOV DX,0005

MOV DX,0005

MOV SI,2000

MOV SI,2000

MOV SI,2000

MOV AX,[SI]

MOV AX,[SI]

MOV AX,[SI]

MOV AX,[SI]

MOV AX,[SI+2]

MOV LOOP

XCHG AX, [SI]

MOV AX, [SI]

| EC6504-Microprocessor and Microcontroller<br>7. LARGEST NUMBER IN AN ARRAY |

|----------------------------------------------------------------------------|

| <b>USING 8086</b>                                                          |

| MOV CX,0004                                                                |

| DEC CX                                                                     |

| MOV SI,2000                                                                |

| MOV AX,[SI]                                                                |

| LABEL CMP AX,[SI+2]                                                        |

| JNC LOOP1                                                                  |

| MOV AX,[SI+2]                                                              |

| LOOP 1 ADD SI,0002                                                         |

| LOOP LABEL                                                                 |

| MOV[2500],AX                                                               |

| HLT                                                                        |

| 9. Write a program based on 8086                                           |

9. Write a program based on 8086 instruction set to compute the average of 'n' numberof bytes stored in the memory.(Nov/ Dec 2012)

| MOV  | SI, 2000H |

|------|-----------|

| MOV  | DI, 3000H |

| MOV  | CL, [SI]  |

| INC  | SI        |

| MOV  | AX, 0000H |

| ADD  | AL, [SI]  |

| JNC  | STEP2     |

| INC  | AH        |

| INC  | SI        |

| LOOP | STEP1     |

| MOV  | [DI]AX    |

| HLT  |           |

|      |           |

Unit-1

8. SMALLEST NUMBER IN AN ARRAY

USING 8086

MOV CX,0004

DEC CX

MOV SI,2000

MOV AX,[SI]

LABEL CMP AX,[SI+2]

JC LOOP1

MOV AX,[SI+2]

LOOP 1 ADD SI,0002

LOOP LABEL

MOV[2500],AX

HLT

10. Write an 8086 ALP to sort the array of elements in ascending order. (Apr/ May 2011, May / June 2013) **MOV SI, 2000H** MOV CL,[SI] DEC CL STEP1 MOV SI,2000H MOV CH, [SI] DEC CH INC SI STEP2 MOV AL, [SI] INC SI CMP AL, [SI] JC STEP3 XCHG AL, [SI] XCHG AL,[SI-1] DEC CH JNZ STEP2 STEP3 DEC CL JNZ STEP1 HLT

| EC6504-Microprocessor a 11. Write an 8086 A | and Microcontroller   | Unit-1                               |     |

|---------------------------------------------|-----------------------|--------------------------------------|-----|

| element in array elem                       | ents. (Apr/ May 2011) |                                      |     |

| MOV S                                       | SI.2000H              | 12. Write an 8086 program to convert | BCD |

| MOV I                                       | DI, 3000H             | data to binary data. (Nov/ Dec 2010) |     |

| MOV (                                       | CL, [SI]              | MOV BX,2000H                         |     |

| INC S                                       | SI                    | MOV AL,[BX]                          |     |

| MOV 4                                       | AL, [SI]              | MOV DL,AL                            |     |

| DEC (                                       | CL                    | AND DL,0FH                           |     |

| STEP1: INC S                                | SI                    | AND AL,F0H                           |     |

| MOV I                                       | BL, [SI]              | MOV CL,4                             |     |

| CMP 4                                       | AL, BL                | ROA AL,CL                            |     |

| JNC S                                       | STEP2:                | MOV DH,OAH                           |     |

| MOV A                                       | AL, BL                | MUL DH                               |     |

| STEP2: DEC                                  | CL                    | ADD AL,DL                            |     |

| JNZ S                                       | STEP1:                | MOV [BX+1],AL                        |     |

| MOV [                                       | [DI],AL               | HLT                                  |     |

| HLT                                         |                       |                                      |     |

#### 7. <u>Linking And Relocation</u>

#### Explain linking and relocation concepts in 8086 Processor.

The DOS linking program links the different object modules of a source program and function library routines to generate an integrated executable code of the source program.

The main input to the linker is the .OBJ file that contains the object modules of the source programs.

The linker program is invoked using the following options.

C> LINK

or

C>LINK MS.OBJ

The output of the link program is an executable file with the entered filename and .EXE extension. This executable filename can further be entered at the DOS prompt to execute the file.

The linked file in binary for *run* on a computer is commonly known as executable file or simply '.exe.' file. After linking, there has to be re-allocation of the sequences of placing the codes before actually placement of the codes in the memory.

The loader program performs the task of reallocating the codes after finding the physical RAM addresses available at a given instant. The DOS linking program links the different object modules of a source program and function library routines to generate an integrated executable code of the source program.

41

The loader program performs the task of reallocating the codes after finding the physical RAM addresses available at a given instant. The *loader* is a part of the operating system and places codes into the memory after reading the '.exe' file.

A program called *locator* reallocates the linked file and creates a file for permanent location of codes in a standard format.

#### Segment combination

In addition to the linker commands, the assembler provides a means of regulating the way segments in different object modules are organized by the linker.

Segments with same name are joined together by using the modifiers attached to the

SEGMENT directives. SEGMENT directive may have the form Segment name SEGMENT Combination-type where the combine-type indicates how the segment is to be located within the load module.

Segments that have different names cannot be combined and segments with the same name but no combine-type will cause a linker error. The possible combine-types are:

**PUBLIC** – If the segments in different modules have the same name and combine type PUBLIC, then they are concatenated into a single element in the load module. The ordering in the concatenation is specified by the linker command.

**COMMON** – If the segments in different object modules have the same name and the combine-type is COMMON, then they are overlaid so that they have the same starting address. The length of the common segment is that of the longest segment being overlaid.

**STACK** – If segments in different object modules have the same name and the combine type STACK, then they become one segment whose length is the sum of the lengths of the individually specified segments. In effect, they are combined to form one large stack.

AT – The AT combine-type is followed by an expression that evaluates to a constant which is to be the segment address. It allows the user to specify the exact location of the segment in memory.

**MEMORY** – This combine-type causes the segment to be placed at the last of the load module. If more than one segment with the MEMORY combine-type is being linked, only the first one will be treated as having the MEMORY combine type; the others will be overlaid as if they had COMMON combine-type.

Source module 1

| DATA | SEGMENT | COM  | MON    |

|------|---------|------|--------|

| DATA | END     | S    |        |

| CODE | SEGN    | MENT | PUBLIC |

| CODE | ENDS    | S    |        |

Source module 2

| DATA | SEGMENT | COMMON |

|------|---------|--------|

|      | •       |        |

|      |         |        |

| DATA | ENDS    |        |

| CODE | SEGMENT | PUBLIC |

|      | ٠       |        |

|      |         |        |

| CODE | ENDS    |        |

|      |         |        |

#### EC6504-Microprocessor and Microcontroller Access to External Identifiers

In order to permit other object modules to reference some of the identifiers in a given module, the given module must include a list of the identifiers to which it will allow access. Therefore, each module in multi-module programs may contain two lists, one containing the external identifiers that can be referred to by other modules.

Two lists are implemented by the EXTRN and PUBLIC directives, which have the forms:

EXTRN Identifier: Type ..., Identifier: Type

and

PUBLIC Identifier,..., Identifier

where the identifiers are the variables and labels being declared or as being available to other modules.

# 8. <u>Stacks</u>

# How stacks are accessed in 8086 processor? Explain briefly.(Dec-2007)

The stack is a block of memory that may be used for temporarily storing the contents of the registers inside the CPU. It is a top-down data structure whose elements are accessed using the stack pointer (SP) which gets decremented by two as we store a data word into the stack and gets incremented by two as we retrieve a data word from the stack back to the CPU register.

The stack is essentially *Last-In-First-Out* (LIFO) data segment. This means that the data which is pushed into the stack last will be on top of stack and will be popped off the stack first.

The stack pointer is a 16-bit register that contains the offset address of the memory location in the stack segment. T Stack Segment register (SS) contains the base address of the stack segment in the memory.

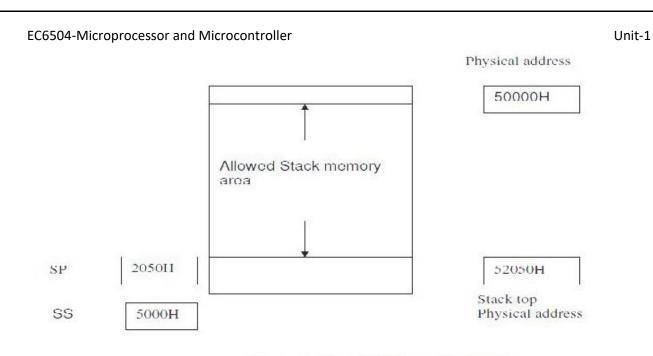

The Stack Segment register (SS) and Stack pointer register (SP) together address the stacktop as explained below:

# SS => 5000H

SP => 2050H

If the stack top points to a memory location 52050H, it means that the location 52050H is already occupied with the previously pushed data. The next 16 bit push operation will decrement the stack pointer by two, so that it will point to the new stack-top 5204EH and the decremented contents of SP will be 204EH. This location will now be occupied by the recently pushed data.

Thus for a selected value of SS, the maximum value of SP=FFFFH and the segment can have maximum of 64K locations. If the SP starts with an initial value of FFFFH, it will be decremented by two whenever a 16-bit data is pushed onto the stack. After successive push operations, when the stack pointer contains 0000H, any attempt to further push the data to the stack will result in stack overflow.

After a procedure is called using the CALL instruction, the IP is incremented to the next instruction. Then the contents of IP, CS and flag register are pushed automatically to the stack. The control is then transferred to the specified address in the CALL instruction i.e. starting address of the procedure. Then the procedure is executed.

Fig. Stack-top address calculation

# 9. <u>PROCEDURES & MACROS</u>

# <u>Macros:</u> AUQ: Define macro. Explain how macros are constructed in ASM-86 with example. (Dec-2010, May2006,10,11)

Macros look like procedures, but they exist only until our code is compiled, after compilation all macros are replaced with real instructions. If we declared a macro and never used it in out code, complier will simply ignore it.

| Macro definition :        |  |  |  |

|---------------------------|--|--|--|

| name MACRO [parameters,]  |  |  |  |

| <statements></statements> |  |  |  |

| ENDM                      |  |  |  |

#### **Example:**

My Macro MACRO P1,P2,P3

MOV AX, P1

MOV BX, P2

MOV CX, P3

ENDM

# Advantages of macros

- Repeated small groups of instructions replaced by one macro

- Errors in macros are fixed only once, in the definition.

- Duplication of effort is reduced.

- In effect, new higher level instructions can be created

- Programming is made easier, less error prone

- Generally quicker in execute than subroutines.

# **Disadvantages of macros**

In large programs, produce greater code size than procedures.

# When to use Macros?

- To replaces small groups of instruction not worthy of subroutines.

- To create a higher instruction set for specific applications.

- To create compatibility with other computers,

- To replace code portions which are repeated often throughout the program.

# **Procedure (PROC)**

This directive marks the start and end of a procedure block called label, the statements in the block can be called with they CALL instruction.

The directive PROC indicated the states of a procedure. The type of the procedure FAR of NEAR is to be specified after the directive, the type NEAR is used to call a procedure with is within the programmed module. The type FAT is used to call a procedure from some other program module. The PROC directive is used with ENDP directive to enclose a procedure.

PROC definition :

label PROC [ [near / far ] ]

<Procedure instructions>

Label ENDP

# Example:

# WEST PROC FAR

-

-

# -

# WEST ENDP

A procedure is a set of instructions that compute some value or take some action (such as printing or reading a character value). The definition of a procedure is very similar to the definition of an algorithm.

#### Unit-1

A procedure is a set of rules to follow which, if they conclude, produce some results. An algorithm is also such a sequence, but an algorithm is guaranteed to terminate whereas a procedure offers no such guarantee.

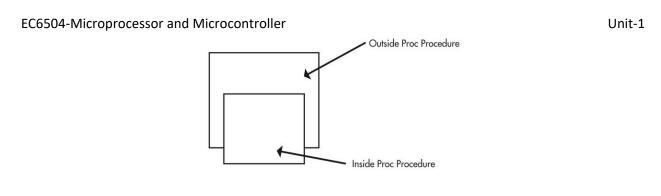

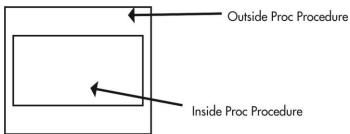

# **Nested Procedures**

The nest procedure is one procedure definition may be totally enclosed inside another. The following is an example of such a pair of procedures:

OUTSIDEPROC PROC NEAR JMP ENDOFOUTSIDE INSIDEPROCPROC NEAR MOC AX, 0 RET INSIDEPROCENDP ENDOFOUTSIDE: CALL INSIDEPROC

MOV BX, 0

RET

OUTSIDEPROC ENDP

Whenever we nest one procedure within another, it must be totally contained within the nesting procedure. That is the PROC and ENDP statements for the nested procedure must lie between the PROC and ENDP directives of the outside, nesting procedure. The following is not legal.

OUTSIDEPROC PROC NEAR

THE OUTISDE proc AND Inside PROC procedures overlap, they are not nested. If we attempt to create a set of procedures like this MASM would report a "block nesting error.

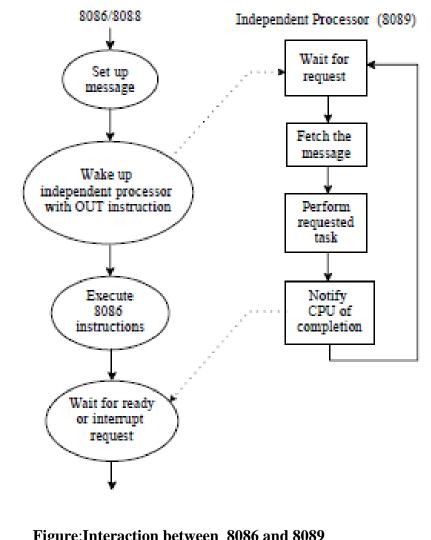

The only form acceptable to MASM